1.编码器

(1)普通编码器

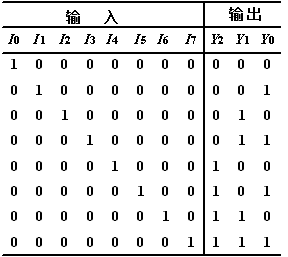

普通编码器中,在某一确定时刻,只能对一个输入信号编码,不允许两个或两个以上的输入信号同时有效,否则将出现乱码。8线-3线普通编码器的功能表如表7.1所示。

表7.1 83编码器的功能表

.

例1.是描述8线-3线普通编码器的Verilog-HDL程序,

module encoder8_3(i0,i1,i2,i3,i4,i5,i6,i7,y2,y1,y0);

input i0,i1,i2,i3,i4,i5,i6,i7;

output y2,y1,y0;

reg y2,y1,y0;

wire [7:0] A;

assign A={i0,i1,i2,i3,i4,i5,i6,i7};

always @(A)

begin

case(A)

8'b00000001: begin y2=1'b0;y1=1'b0;y0=1'b0; end

8'b00000010: begin y2=1'b0;y1=1'b0;y0=1'b1; end

8'b00000100: begin y2=1'b0;y1=1'b1;y0=1'b0; end

8'b00001000: begin y2=1'b0;y1=1'b1;y0=1'b1; end

8'b00010000: begin y2=1'b1;y1=1'b0;y0=1'b0; end

8'b00100000: begin y2=1'b1;y1=1'b0;y0=1'b1; end

8'b01000000: begin y2=1'b1;y1=1'b1;y0=1'b0; end

8'b10000000: begin y2=1'b1;y1=1'b1;y0=1'b1; end

default: begin y2=1'b1;y1=1'b1;y0=1'b1; end

endcase

end

endmodule

(2)优先编码器

优先编码器中,同一时刻可以允许两个或两个以上输入信号同时有效。不过,在设计优先编码器时,需要将所有的输入信号按优先顺序排队,如果几个输入信号同时出现时,只对优先权最高的一个信号进行编码。与用普通门电路实现的优先编码器不同的是,优先级的顺序可以很方便的修改。

表7.2 4线-2线优先编码器的功能表 | ||||||

输入 | 输出 | |||||

E | I0 | I1 | I2 | I3 | Y1 | Y0 |

1 | × | × | × | × | 0 | 0 |

0 | × | × | × | 1 | 1 | 1 |

0 | × | × | 1 | 0 | 1 | 0 |

0 | × | 1 | 0 | 0 | 0 | 1 |

0 | 1 | 0 | 0 | 0 | 0 | 0 |

例2是描述4线-2线优先编码器的Verilog-HDL程序

module encoder4_2(E,I0,I1,I2,I3,Y1,Y0);

input E,I0,I1,I2,I3;

output Y1,Y0;

reg Y1,Y0;

always @(E,I0,I1,I2,I3)

begin

if (E) begin Y1=1'b0;Y0=1'b0; end

else if (I3) begin Y1=1'b1;Y0=1'b1; end

else if (I2) begin Y1=1'b1;Y0=1'b0; end

else if (I1) begin Y1=1'b0;Y0=1'b1; end

else if (I0) begin Y1=1'b0;Y0=1'b0; end

else begin Y1=1'b0;Y0=1'b0; end

end

endmodule

2.译码器

译码是编码的逆过程,也就是把一个二进制代码表示的信息翻译出来。译码器的输入为n位二进制代码,输出为2n个表征代码原意的状态信号,2n个输出信号中有且只有一个是有效的。表7.3是3线-8线译码器对应的功能表。

表7.3 3线-8线译码器的功能表 | ||||||||||||

输入 | 输出 | |||||||||||

S1 | S2+S3 | A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

0 | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

× | 1 | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

例3是描述3线-8线译码器的Verilog-HDL程序,其中S1,S2,S3,是对应的使能端,S1为1,同时S2,S3为0时输入信号有效。

module decoder3_8(S1,S2,S3,A2,A1,A0,Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0);

input S1,S2,S3,A2,A1,A0;

output Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0;

wire S;

wire [2:0] A;

reg [7:0] Y;

assign S=S2 | S3;

assign A={A2,A1,A0};

always @(A,S1,S)

begin

if (S1 && !S) begin

case(A)

3'b000: Y=8'b11111110;

3'b001: Y=8'b11111101;

3'b010: Y=8'b11111011;

3'b011: Y=8'b11110111;

3'b100: Y=8'b11101111;

3'b101: Y=8'b11011111;

3'b110: Y=8'b10111111;

3'b111: Y=8'b01111111;

default: Y=8'b11111111;

endcase

end

else begin Y=8'b11111111;

end

end

assign Y0=Y[0];

assign Y1=Y[1];

assign Y2=Y[2];

assign Y3=Y[3];

assign Y4=Y[4];

assign Y5=Y[5];

assign Y6=Y[6];

assign Y7=Y[7];

endmodule