* 数字电子技术实验课程介绍

* 综合设计项目预览(任选1题)

- 2.1交通灯控制电路设计

- 2.1.1 项目背景

- 2.1.2 系统分析及功能模块划分

- 2.2简易数字频率计设计

- 2.2.1 项目背景

- 2.2.2 系统分析及功能模块划分

- 2.3跑马灯电路设计

- 2.3.1 项目背景

- 2.3.2 系统分析及功能模块划分

* 实验三 用Verilog—HDL语言设计组合逻辑电路

数字电子技术实验

青岛大学

一、课程的地位和作用

《数字电子技术实验》是《数字电子技术》课程的重要实践环节之一。通过设计电路,仿真验证,安装与调试电路,查找与排除电路故障,信号测量,撰写实验报告,互助讨论等环节,培养学生运用理论解决实际问题的能力,提高学生动手操作能力、创新能力和工程实践能力。

二、教学目标

1、掌握数字实验装置及常用仪器设备的正确使用方法;

2、掌握常用中小规模数字电路集成器件的特性及使用方法;

3、初步掌握可编程逻辑器件的使用方法及EDA技术;

4、学会合理布线和正确连接线路,有效读取实验数据并会判断实验结果的合理性;

5、能对实验线路进行调试和故障排除;

6、能根据需要选择合理的器件,并会查阅各种相关技术手册和资料。

三、课程的主要内容与特点

数字电子技术实验主要由数字电路集成器件的使用方法、组合逻辑电路设计、时序逻辑电路设计和EDA技术四部分组成。数字电子技术实验与电路实验、模拟电子技术实验的侧重点有所不同。电路实验、模拟电子技术实验注重的是测量方法,误差的分析,而数字电子技术实验注重的是输入、输出信号在逻辑与时序上的关系。数字电路的设计具有灵活多变的特点,这就要求在设计数字电路时,要开阔思路,选择最简单、最容易实现的方法。* 数字电子技术实验课程介绍

* 综合设计项目预览(任选1题)

* 实验三 用Verilog—HDL语言设计组合逻辑电路

1. Quartus II 编程环境的使用练习,验证4线-2线优先编码器。

2. 用Verilog HDL语言设计一个8线-3线优先编码器。

表7.4 8线-3线优先编码器的功能表 | |||||||||||||

输入 | 输出 | ||||||||||||

S | I0 | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Y2 | Y1 | Y0 | YS | YEX |

1 | × | × | × | × | × | × | × | × | 1 | 1 | 1 | 1 | 1 |

0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

0 | × | × | × | × | × | × | × | 0 | 0 | 0 | 0 | 1 | 0 |

0 | × | × | × | × | × | × | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

0 | × | × | × | × | × | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

0 | × | × | × | × | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

0 | × | × | × | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

0 | × | × | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

0 | × | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

3. 用Verilog HDL语言设计一个二-十进制译码器。

表7.5 二十进制译码器的功能表 | ||||||||||||||

序列 | 输入 | 输出 | ||||||||||||

A3 | A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

4 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

5 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

6 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

10-15 | 1010-1111为伪码 | 输出端全部无效,既全为逻辑1 | ||||||||||||

4. 用Verilog HDL语言设计一个满足下表要求的组合逻辑电路。

| 输入 | 输出 | ||||||

| IN2 | IN1 | R1 | Y1 | G1 | R2 | Y2 | G2 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

(1)以实际应用为背景,导入题目,建立系统概念,明确学习目的,提高学习兴趣。

(2)化整为零,分模块、分阶段完成实验任务

根据数字电路初学者的特点,遵循兴趣引导,由浅入深,循序渐进的教学规律,将系统划分为若干相对简单,易于理解的小模块,分配到相应的教学单元中去完成。

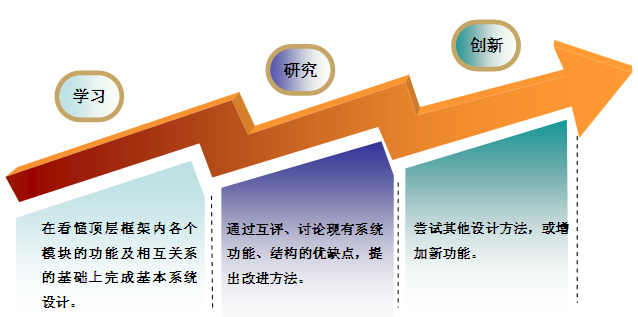

(3)教学内容分层次递进

(4)仿真实验与实物实验相结合

本着“能实不虚”的原则,在课堂上进行实物实验,在课下预习阶段采用远程虚拟实验室,为学生提供一个贴近实际实验室环境的虚拟实验平台,使学生在不进入实验室的情况下就能练习仪器设备的使用,甚至做实验,既提高学习兴趣,也提高在实验室做实验的效率。